#0. Modelsim 설치하기, Compile 하는 방법-intel Quartus

Verilog/Verilog 실습 2023. 8. 17. 22:17이제 Verilog 문법을 모두 안다고 가정한 상태에서 여러가지 모듈들을 실습을 통해 만들어보도록 하자.

가장 먼저 해야할 것은 시뮬레이션을 돌리는 것인데, 만들어낸 verilog 코드를 테스트벤치를 통해 시뮬레이션을 한 후 회로를 합성하게 된다. 즉, 시뮬레이터와 합성기 이렇게 두가지 프로그램이 필요한데, 이번 글에서는 intel사에서 제공하고 있는 quartus를 활용하여 시뮬레이터를 먼저 설치해보도록 하겠다.

이 quartus를 설치하면 Modelsim 과 Quartums가 설치되는데, 여기서 Modelsim이 시뮬레이터 역할을 하게 된다

1. 설치링크

Intel® Quartus® Prime Lite Edition Design Software Version 20.1.1 for Windows

Intel® Quartus® Prime Lite Edition Design Software Version 20.1.1 B720 for Windows

www.intel.com

이전에는 지멘스 사에서 무료로 제공했던 것으로 기억하는데 현재는 intel 사에서 제공한다. 라이센스가 있으면 다양한 기능들을 제공하지만, 일단은 무료버전으로 사용하기로 한다.

위 홈페이지를 들어가면

이렇게 다운로드가 가능하고 받은 압축 파일을 풀어서 setup.bat를 실행시키고 잠시 기다리면 된다. 용량이 6기가 정도로 크기 때문에 wifi를 이용해서 다운받기를 바란다. 설치하는데에는 시간이 좀 걸린다.

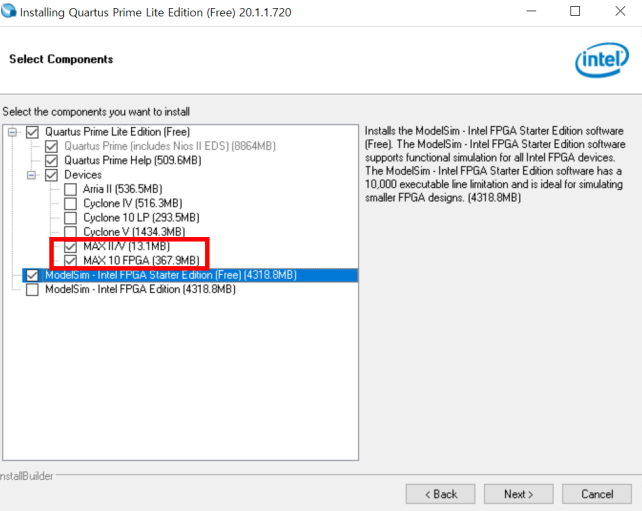

modelsim의 starter 버전으로 설치한다.

설치시에는 디렉토리 경로에 한글이 포함되지 않도록한다.(오류가 많이 난다.)

device를 선택할 수 있는데, 이는 어떤 FPGA로 가상의 시뮬레이션을 돌릴 수 있도록 할지 결정하는 것이다. 간단한 모듈들은 위 두 체크만 해도 돌릴 수 있으니 용량이 부족하다면 모두 체크할 필요는 없다. next를 누르면 설치가 시작되고 약 10~15분 정도 시간 뒤에 설치가 완료된다.

2. 프로젝트 관리 및 compile 하기

그리고 modelsim을 시작에서 찾아 실행시키면

위 화면을 확인할 수 있다.(필자는 이미 시뮬레이션을 해봐서 이런 창인데, 프로젝트가 안열린 상태라면 조금 다를수도 있다.) 여기서 왼쪽 상단에 file-new-project..에 들어가면

프로젝트를 생성할 수 있는데, project Name에는 원하는 프로젝트 명을(영어로)

location 역시 자신이 원하는 경로에 영어로 사용하면 되며, Default Library name은 프로젝트 생성시 만들어지는 기본 폴더 이다. ok를 눌러 다음으로 가면

이런 창이 뜨는데 여기서 create new file을 클릭하면 Verilog 확장자를 가진 v 파일을 추가할 수 있다.

이런 창이 뜨면 원하는 모듈의 이름.V형식으로 파일이름을 결정하고, 아래쪽 왼쪽에는 파일 타입을 결정할 수 있다. 우리는 verilog 이므로 verilog를 선택하여 파일을 추가해주면 된다.

이렇게 test.v 와 test_tb.v를 만들어주면

이런 창을 확인할 수 있고, 이곳이 project를 관리하는 창이 되겠다. project 내부에 모듈들과 테스트벤치를 확인할 수 있으며 현재 status 부분에는 물음표가 되어 있는데 이는 차후 코드를 모두 작성하고, 컴파일 하게 되면 체크표시로 바뀌게 된다.

Compile은 여기서 오른쪽 마우스를 눌러서 compile all을 누르던지 아니면 메뉴바에 compile에서 해도 된다.

Compile all을 하게 되면 위와같이 체크표시가 되며, 아래쪽 transcript에서는 컴파일이 잘 됬는지 등의 콘솔창을 확인할 수 있다.

만약 위와 같은 창들이 안보인다면, 상단 메뉴바에 view를 눌러보면 원하는 창들을 꺼낼 수 있도록 되어있다.

다음 글에서 시뮬레이션 하는 방법을 이어서 알아보도록 한다.